## Measurement-Based Model Parameters for Quasi-Optical Electron Device Arrays

L. B. Sjogren, H.-X. L. Liu, X.-H. Qin,

C. W. Domier and N. C. Luhmann, Jr.

**Abstract**—Impedance element values for a Schottky beam control diode array are obtained by curve-fitting quasi-optical reflection coefficient measurements to a series *RLC* array model. The model provides a good representation of the array behavior. Parameters of Schottky varactor arrays tested to-date are summarized. The technique should be applicable to other quasi-optical arrays, as well.

### I. INTRODUCTION

Planar arrays of integrated semiconductor devices have attracted recent interest as solid state components for high frequency quasi-optical applications. In order to fully realize the potential of quasi-optical device arrays, accurate models must be developed. Successful models for high frequency electron devices have been obtained by “de-embedding” the elements of a physical model from measured device behavior (e.g. measured *S* parameters). This procedure is equally applicable to quasi-optical arrays. In [1], the model parameters of a Schottky varactor diode array were successfully extracted from complex transmission coefficient measurements. In the current paper, we perform a similar parametric extraction on a new array by the use of complex reflection coefficient measurements, and summarize the performance of Schottky varactor diode arrays tested to-date.

### II. CHARACTERIZATION

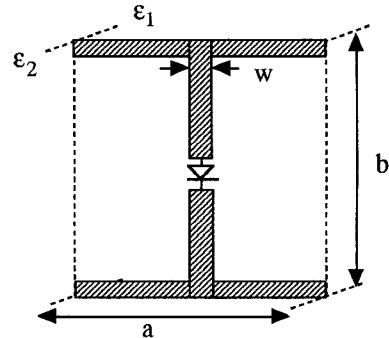

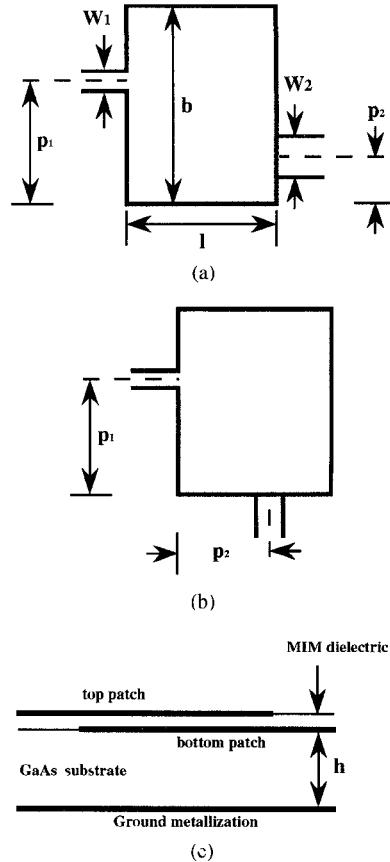

The behavior of a diode array (whose unit cell is illustrated in Fig. 1) can be represented by a shunt impedance across a transmission-line representing a (normally-incident) propagating beam whose electric field is parallel to the diode embedding strip. For the varactor array, the impedance consists of an inductor (due to the strip) in series with a capacitor and resistor (the latter two primarily associated with the diode). In [1], the values of *R*, *L*, and *C* in this series-resonant model were obtained for a varactor array denoted “PS1” by extraction from quasi-optical transmission coefficient measurements.

A new array, denoted “PS2”, with 7000 operational “ABD” [2] Schottky diode varactors, has been characterized here by use of reflection coefficient measurements. (Dimensions of the PS2 array are  $a = 300 \mu\text{m}$ ,  $b = 120 \mu\text{m}$ , and  $w = 10 \mu\text{m}$ . Further details on the design and functional operation of the array can be found in [3], [4].) The phase of the reflection coefficient was obtained by the method of [5]. In this technique, a portion of the incident beam is aligned perpendicular to the diode embedding strips, serving as a reference beam. The reflection phase for the “active” beam (polarized parallel to the diode strips) can then be determined by examining the polarization state of the reflected beam. The amplitude is obtained by comparison of the reflected beam power versus that at a frequency for which there is no attenuation, with a beam component polarized

Manuscript received April 23, 1993; revised August 1, 1994. This work was supported in part by the Joint Services Electronics Program, contract F4962 092-C-0055, the U.S. Department of Energy, Northrop Corp., and the California MICRO program.

The authors were with the Department of Electrical Engineering, University of California, Los Angeles, CA 90024-1594 USA.

IEEE Log Number 9408584.

Fig. 1. Schematic illustration of a beam control array unit cell. A normally incident beam, with vertically polarized electric field, induces a current through the vertical strip and diode. The horizontal (bias) lines have essentially no effect on array behavior.

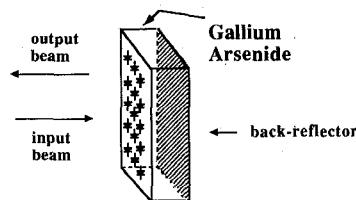

perpendicularly to the “active” array axis employed as an amplitude reference to account for variation of incident beam power versus frequency. The array configuration for the reflection tests is shown in Fig. 2.

#### A. Array Resistance

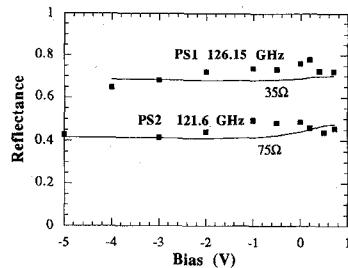

At frequencies for which the thickness of the reflector-backed substrate equals an odd multiple of a quarter wavelength, the array impedance appears directly as a load termination. At this frequency, reflection amplitude is a much stronger function of array resistance than array reactance. The measured power reflectance of the PS2 array is shown on Fig. 3. Comparison with curves obtained by transmission-line circuit simulation (using approximate estimates for *L* and *C*) shows that a “fit” is obtained for a PS2 array resistance of approximately  $75 \Omega$ . The same test, applied to a PS1 array, shows an approximate resistance of  $35 \Omega$ . This agrees closely with the transmission test result [1] of  $40 \Omega$ . The high resistance of the PS2 array was due to extreme thinning of the Schottky anode metallization, which was verified by microprobe measurement of the DC resistance of the Schottky anodes on typical diodes. These measurements indicated an anode finger resistance of  $12 \Omega$ . With two anode fingers per ABD, and the array resistance due to the array device being that of the individual device times the aspect ratio of the unit cell,  $a/b$  [6], the anode finger will contribute  $60 \Omega$  to the array resistance, dominating the array resistance. The resistance of a well-fabricated ABD should be very low; design and process modifications are proposed in [2] which should assist in achieving a low resistance ABD.

#### B. Array Inductance

Parameter extraction for the PS1 array showed [1] that the inductance obtained by electromagnetic simulation is very accurate. Thus, for the PS2 array, the simulated value of  $160 \text{ pH}$  has been assumed.

#### C. Array Capacitance

Measurements of reflectance and reflection coefficient phase were taken at three frequencies centered at the “flat amplitude frequency”. The array capacitance was determined as the value which, employed in a quasi-optical transmission line circuit simulation, provides a least-squares fit with the measured results. The fitting was performed independently for the set of reflectance and reflection phase curves.

Fig. 2. Array configuration for reflection testing. Addition of a "shim" layer of GaAs gives a nominal array thickness of 0.838 mm. Behavior of the array indicated actual thickness of 0.851 mm, and this value was assumed for model parameter fitting.

Fig. 3. Beam reflectance for the PS1 and PS2 arrays at the "flat amplitude" frequency (PS1: 126.15 GHz, PS2: 121.6 GHz). Markers indicate measured values; lines indicate the simulated results with "best fit" model parameters.

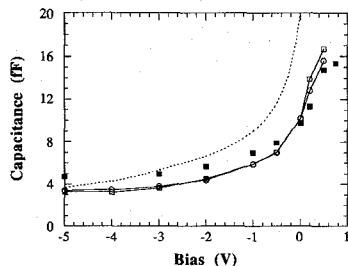

Fig. 4. C-V characteristics for the PS2 array. Dotted line: original one-dimensional simulation. Solid line (hollow squares): 1-MHz C-V curve for typical array diode. Solid line (hollow circles): 1-MHz C-V curve for typical array diode. Solid line (solid circles): 1-MHz C-V characteristic of an "array bias unit" [4] (group of contiguous rows of diodes), with coplanar strip capacitance subtracted [1], scaled to a single diode. All three curves are divided by the aspect ratio  $a/b$  for direct comparison with the quasi-optical C-V results, which are shown by solid markers.

The two resultant extracted C-V curves agreed well. The "true" C-V curve was taken as the average of the two. In Fig. 4, the extracted C-V curve is shown, along with that of the original simulation (one dimensional solution for Poisson's equation) and the results for a typical diode measured at 1 MHz with a C-V meter (measured as described in [1]).

### III. CONCLUSION

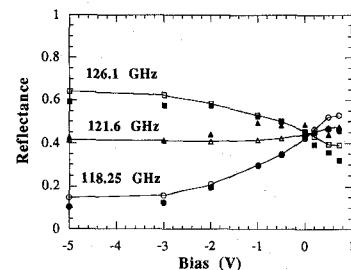

Figs. 5 and 6 show that the  $RLC$  array model, with "best fit" parameters, provides a good representation of the array behavior. The greatest deviation is for the phase at negative bias, where a small change (or error) in capacitance results in a large phase difference. These results show that reflection coefficient measurements can be successfully employed in the parametric characterization of quasi-optical active arrays. Desirable future extensions include the use of measurements at a larger number of frequencies, including more elements for a more precise model, and the extension of the procedure for more complex arrays, such as amplifier arrays [7].

Fig. 5. Beam (power) reflectance curves for the PS2 array. Solid markers indicate measured values; lines indicate the simulated results with "best fit" model parameters.

Fig. 6. Reflected beam phase curves for the PS2 array. Solid markers/dashed lines indicate measured values; hollow markers/solid lines indicate the simulated results with "best fit" model parameters. Phase is with respect to a reference plane at the air to GaAs interface, and is relative to that of an orthogonally polarized beam (3.08 radians).

TABLE I

MODEL PARAMETERS OF THE BEAM CONTROL ARRAYS. \*TWO ARRAYS WERE TESTED; HOWEVER, C-V CURVES ARE AVAILABLE ONLY FOR THE ARRAY WITH THE HIGHER RESISTANCE

| Design | $C_{min}$ (fF) | $c_{rd}$ | $\eta_{q0}$ | $R_{array}$ ( $\Omega$ ) |

|--------|----------------|----------|-------------|--------------------------|

| [8]    | 17.5           | 3.29     | 0.630       | 78, 26*                  |

| PS1    | 4.9            | 6.35     | 0.395       | 35                       |

| PS2    | 4.7            | 5.12     | 0.613       | 75                       |

Performance-related parameters for Schottky varactor arrays fabricated to-date are summarized in Table I. Estimated values from the original proof-of-principle experiment [8] are included. A useful performance parameter is the ratio of array capacitance ratio,  $c_{r,a}$ , ( $c_r = C_{max}/C_{min}$ ) to diode capacitance ratio,  $c_{r,d}$ , which we denote the quasi-optical efficiency,  $\eta_{q0}$ . (Note that  $c_{r,a}$  is based on the slightly larger maximum useable bias obtainable at the millimeter-wave frequency versus that for the 1 MHz C-V test, due to the smaller relative conductance versus capacitive susceptance at the higher frequency). The quasi-optical efficiency can be considered a gauge of how effectively the performance range of the diode is achieved by the array as a whole. Its value is considerably better for the PS2 array than the PS1 array, which is consistent with the achievement of greater capacitance uniformity over the array and lower incidence of faulty cells [3]. Both arrays achieve a very low minimum capacitance (approximately 5 fF), which can be attributed to the rectangular unit cell design [6].

### REFERENCES

- [1] L. B. Sjogren, H.-X. L. Liu, F. Wang, T. Liu, X.-H. Qin, W. Wu, E. Chung, C. W. Domier, and N. C. Luhmann, Jr., "A monolithic diode array millimeter-wave beam transmittance controller," *IEEE Trans. Microwave Theory Tech.*, vol. 41, no. 10, pp. 1782-1790, Oct. 1993.

- [2] —, "Electronic and electromagnetic devices for millimeter-wave beam control arrays," *Int. J. Infrared and Millimeter Waves*, vol. 14, no. 6, pp. 1201–1216, June 1993.

- [3] L. B. Sjogren, "Diode array beam controllers," Ph.D. dissertation, Electrical Engineering Department, UCLA, 1993.

- [4] L. B. Sjogren, H.-X. L. Liu, X.-H. Qin, C. W. Domier, and N. C. Luhmann, Jr., "Phased array operation of a diode grid impedance surface," *IEEE Trans. Microwave Theory Tech.*, vol. 42, no. 4, pp. 565–572, Apr. 1994.

- [5] L. B. Sjogren, H.-X. L. Liu, and N. C. Luhmann, Jr., "A polarization approach for quasi-optical phase measurement," *Microwave and Optical Technol. Lett.*, vol. 5, no. 12, pp. 623–627, Nov. 1992.

- [6] L. B. Sjogren and N. C. Luhmann, Jr., "An impedance model for the quasi-optical diode array," *IEEE Microwave and Guided Wave Lett.*, vol. 1, no. 10, pp. 297–299, Oct. 1991.

- [7] M. Kim, J. J. Rosenberg, R. P. Smith, R. M. Weikle, II, J. B. Hacker, M. P. Delisio, and D. B. Rutledge, "A grid amplifier," *IEEE Microwave and Guided Wave Lett.*, vol. 1, no. 11, pp. 322–324, 1991.

- [8] W. W. Lam, C. F. Jou, N. C. Luhmann, Jr., and D. B. Rutledge, "Millimeter-wave diode-grid phase shifters," *IEEE Trans. Microwave Theory Tech.*, vol. 36, no. 5, p. 902, 1988.

## MIM Capacitor Modeling: A Planar Approach

Giancarlo Bartolucci, Franco Giannini,

Ernesto Limiti, and Steven P. Marsh

**Abstract—**On the basis of a planar approach, an equivalent circuit model of MMIC overlay capacitors with feeding lines in generic position has been derived. Closed expressions for the equivalent circuit elements are presented. The validity of the proposed circuit has been successfully tested with experimental data. Its simplicity and flexibility makes it attractive for implementation in CAD packages.

### I. INTRODUCTION

Metal–Insulator–Metal (MIM) capacitors are key elements in many microwave and millimeter-wave monolithic integrated circuits. DC-blocks, matching sections, and biasing circuitry widely utilize this component. An accurate model of the structure is therefore crucial for any MMIC design. Many monolithic foundries have developed their own proprietary models by means of parameter extraction methods from experimental data. The so-obtained models are too device-specific and their validity is restricted to the frequency range of the fitting measurements. Other approaches, closer to the physical structure of the MIM capacitor, have been previously presented, resulting in a distributed [1] or lumped [2] equivalent model. Both approaches are zero- or mono-dimensional and therefore do not take into account the intrinsic planar behavior of the structure, demonstrated in [3] and [4]. Such a planar behavior must be accounted for when, due to layout constraints, the designer is forced to feed the capacitor with off-centered ports or even positioned on perpendicular sides of the structure.

Manuscript received January 17, 1994; revised July 19, 1994.

G. Bartolucci, F. Giannini, and E. Limiti are with the Department of Electronic Engineering, University of Roma "Tor Vergata," Via della Ricerca Scientifica s.n.c., 00133 Rome, Italy.

S. P. Marsh is with the GaAs IC Department, GEC Marconi Materials Technology Limited, Caswell Towcester, Northamptonshire, United Kingdom. IEEE Log Number 9408577.

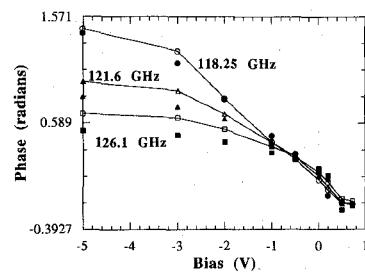

Fig. 1. The MIM capacitor: (a) top view for feeding lines on opposite sides; (b) perpendicular sides; and (c) section of the structure.

Moreover, design considerations suggest the development of a circuit model of the MIM capacitor that can be easily implemented in commercial CAD packages. To fulfill these requirements, in this paper a novel circuit model, based on a planar approach, for two-port overlay capacitors is presented. The model accounts for the effects of generic port positioning: the ports can be placed on opposite sides of the structure and off-centered or even on perpendicular sides. Simple and closed-form expressions for the model elements are provided. The proposed model has been successfully tested comparing the simulated results to experimental data in a wide frequency band.

### II. THE EQUIVALENT CIRCUIT

The typical structure of an MIM capacitor is shown in Fig. 1. The prevailing effect at very low frequencies is by far the capacitive one: it can be easily represented by a series-connected parallel-plate capacitor. As frequency increases, planar effects due to the bottom patch, which are not taken into account by this simple model, become evident, altering the ideal capacitive behavior. This leads us to model the whole structure as a cascade connection of the main series capacitor ( $C_{MIM}$ , whose value can be computed as if it were a parallel-plate capacitor) and of the bottom patch, added to account for the above-mentioned planar effects.

As already well established (see [5]), the external behavior of such a planar structure can be modeled in terms of a  $Z$ -matrix description. The entries  $Z_{ij}R$  are obtained enclosing the patch by lateral magnetic walls and expanding the EM field inside the resulting resonator into